Cadence Digital and Custom Flows Achieve Certification for TSMC N3 Process

August 25 2020 - 8:45AM

Business Wire

Companies broaden collaboration to continue

advancing mobile, AI and hyperscale electronics innovation

Cadence Design Systems, Inc. (Nasdaq: CDNS) today announced that

its digital full flow and custom tool suite has been optimized for

TSMC’s 3nm (N3) process technology. The Cadence® tools have

achieved the latest Design Rule Manual (DRM) and SPICE

certification for TSMC’s N3 process. These innovations assist in

driving and delivering next-generation mobile, AI and HPC

applications, developed on the N3 process technology, with

innovative reference flows and methodologies. Cadence and TSMC

continue to work closely with customers on production designs on

TSMC’s advanced-process technologies.

The certified tool suites support the Cadence Intelligent System

Design™ strategy, enabling customers to achieve SoC design

excellence. Cadence’s integrated digital and custom flow is fully

convergent and all tools work together seamlessly. Customers can

download the corresponding N3 process design kit (PDK) to begin

design projects now. To learn more about the Cadence advanced-node

solutions, visit www.cadence.com/go/adnnodesolspr.

N3 Digital and Signoff Tool Suite Certification

The Cadence integrated digital full flow has been updated and

certified for use on TSMC’s N3 process technology. The flow

features enhanced physical optimization and timing signoff closure.

It includes the Innovus™ Implementation System, Liberate™

Characterization, Liberate Variety™ Statistical Characterization,

Quantus™ Extraction Solution, Tempus™ Timing Signoff Solution,

Voltus™ IC Power Integrity Solution and Pegasus™ Verification

System. Additionally, the Genus™ Synthesis Solution and its

predictive iSpatial technology is enabled for these process

technologies for mobile, AI and hyperscale designs.

The Cadence digital suite and available reference flows help

customers achieve better power, performance and area (PPA) while

designing on TSMC’s N3 process. Some of the tool suite enhancements

that enable customers to successfully design mobile, AI and HPC

systems with improved PPA include, improved extraction accuracy,

updated routing rules, accurate LVF-generation during

characterization and robust support of advanced coloring.

N3 Custom Tool Suite Certification

The Cadence custom tool suite has been certified on TSMC’s N3

process. The certification includes the Virtuoso® Custom IC design

platform, consisting of the Virtuoso Schematic Editor, Virtuoso

Layout Suite and Virtuoso ADE Product Suite, the Voltus-Fi Custom

Power Integrity Solution, and the Spectre® Circuit Simulation

Platform, which includes the Spectre X Simulator.

Cadence has continuously improved its custom design

methodologies and capabilities within the Virtuoso Advanced-Node

Platform for use with TSMC’s advanced-process technologies.

Customers continue to achieve better custom design throughput

versus traditional design methodologies using the advanced

capabilities within the Virtuoso platform. Custom enhancements for

TSMC’s N3 process technology include expanded 3nm design rule

support, custom digital color remastering, enhanced analog cell

support, additional productivity improvements with an enhanced

device-level P&R flow and a front-to-back legacy-node design

migration flow.

“By continuing to extend our collaboration with Cadence, we’re

providing support for our customers that are designing the next

generation of mobile, AI and HPC systems using our latest N3

process,” said Suk Lee, senior director of the Design

Infrastructure Management Division at TSMC. “Our latest work

enables our customers to design with the tools, benefitting from

the significant power and performance boost of TSMC’s 3nm process

technology and to quickly launch their new product innovations to

market.”

“We’ve continued to work closely with TSMC to enable our

customers to take advantage of the most advanced technologies

required to support today's emerging mobile, AI and HPC

applications,” said Dr. Chin-Chi Teng, senior vice president and

general manager of the Digital & Signoff Group at Cadence.

“Based on latest N3 certification from TSMC and our joint successes

with customers on N7 and N5 designs, customers are now evaluating

our digital reference flow on TSMC’s N3 process technology to take

their designs to the next level.”

About Cadence

Cadence is a pivotal leader in electronic design, building upon

more than 30 years of computational software expertise. The company

applies its underlying Intelligent System Design strategy to

deliver software, hardware and IP that turn design concepts into

reality. Cadence customers are the world’s most innovative

companies, delivering extraordinary electronic products from chips

to boards to systems for the most dynamic market applications

including consumer, hyperscale computing, 5G communications,

automotive, aerospace, industrial and healthcare. For six years in

a row, Fortune Magazine has named Cadence one of the 100 Best

Companies to Work For. Learn more at cadence.com.

© 2020 Cadence Design Systems, Inc. All rights reserved

worldwide. Cadence, the Cadence logo and the other Cadence marks

found at www.cadence.com/go/trademarks are trademarks or registered

trademarks of Cadence Design Systems, Inc. All other trademarks are

the property of their respective owners.

View source

version on businesswire.com: https://www.businesswire.com/news/home/20200825005427/en/

For more information, please contact: Cadence Newsroom

408-944-7039 newsroom@cadence.com

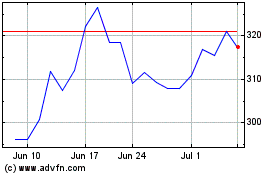

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Mar 2024 to Apr 2024

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Apr 2023 to Apr 2024