Cadence Digital and Signoff Full Flow and Custom/Analog Tools Certified for TSMC N6 and N5/N5P Process Technologies

September 25 2019 - 8:45AM

Business Wire

Highlights:

- Cadence tools certified for the latest version of N6 and N5/N5P

DRM and SPICE models

- TSMC and Cadence collaborating with customers on N6 design

starts; customers in full production development with multiple test

chips completed

- Active N5P customer engagements underway

- Collaboration advancing the development of next-generation

mobile applications

Cadence Design Systems, Inc. (NASDAQ: CDNS) today announced that

its digital and signoff full flow and custom/analog tools have

achieved certification on TSMC’s N6 and N5/N5P process

technologies. The Cadence® tools have attained the latest N6 and

N5/N5P Design Rule Manual (DRM) and SPICE certification, advancing

next-generation mobile application development. Cadence and TSMC

are working with customers on N6 design starts both on production

designs and test chips. Additionally, Cadence and TSMC have active

N5/N5P customer engagements underway.

The certified tools support the Cadence Intelligent System

Design™ strategy, enabling customers to achieve SoC design

excellence. Cadence’s integrated flow ensures that all the tools

will work together seamlessly, and customers can download the

corresponding N6 and N5/N5P process design kits (PDKs) to begin

design projects now. To learn more about the Cadence digital and

signoff solutions for advanced nodes, visit

www.cadence.com/go/dsn6n5poip. For information about the Cadence

custom/analog solutions, visit www.cadence.com/go/can6n5poip.

N6 and N5/N5P Digital and Signoff Tool Certification

Cadence delivered a fully integrated digital implementation and

signoff tool flow, which has been certified on both TSMC’s N6 and

N5/N5P process technologies. The Cadence full flow includes the

Innovus™ Implementation System, Liberate™ Characterization,

Liberate Variety™ Statistical Characterization, Quantus™ Extraction

Solution, Tempus™ Timing Signoff Solution, Voltus™ IC Power

Integrity Solution and Pegasus™ Verification System. Additionally,

the Genus™ Synthesis Solution is enabled for these process

technologies.

The Cadence digital and signoff tools provide EUV support across

the flow, offering customers optimal power, performance and area

(PPA). Some of the latest Cadence tool enhancements include

expanded EUV layer support and back end of line (BEOL) layer

modeling and middle end of line (MEOL) features.

N6 and N5/N5P Custom/Analog Tool Certification

The Cadence custom/analog tools certified on TSMC’s N6 and

N5/N5P process technologies include the Spectre® Accelerated

Parallel Simulator (APS), Spectre X, Spectre eXtensive Partitioning

Simulator (XPS), Spectre RF Option, Spectre Circuit Simulator, and

Voltus-Fi Custom Power Integrity Solution, as well as the Virtuoso®

custom IC design platform, which consists of the Virtuoso Schematic

Editor, Virtuoso Layout Suite and Virtuoso ADE Product Suite.

With the latest design methodologies and capabilities included

with the Virtuoso Advanced Node Platform on TSMC’s advanced process

technologies, customers can achieve better custom physical design

throughput versus traditional non-structured design methodologies

via the advanced capabilities in the Virtuoso and Spectre

tools.

Custom/analog enhancements for TSMC’s advanced process

technologies incorporate an accelerated custom placement and

routing methodology, which enables customers to improve

productivity and meet power, density and electro migration

requirements. Universal polygrid snapping and color engine support

features have been enabled in N6. Additionally, expanded design

rule constraint support with area-based rule, asymmetric coloring

rule, voltage-dependent rule (VDR) and analog cell support,

including guardring and dummy insertion are enabled for N5/N5P.

“Our ongoing collaboration with Cadence ensures that our

customer’s requirements for design solutions and services are

well-addressed and supported,” said Suk Lee, TSMC senior director,

Design Infrastructure Management Division. “The joint efforts

combining TSMC’s most advanced process technologies and our

partners’ certified design tools can empower our customers to

capture growth opportunies with faster time-to-market and

successful silicon innovations for next-generation mobile

application development.”

“We’ve broadened our collaboration with TSMC to include support

for its advanced N5/N5P process technologies, enabling our

customers to achieve optimal PPA results with our tools,” said Dr.

Chin-Chi Teng, senior vice president and general manager of the

Digital & Signoff Group at Cadence. “We’ve also achieved

certification for N6 early design starts and are ready to support

any customer transitioning from the N7 process technology who

requires even more competitive advantages to deliver the most

innovative, complex designs in a timely manner.”

About Cadence

Cadence enables electronic systems and semiconductor companies

to create the innovative end products that are transforming the way

people live, work and play. Cadence software, hardware and

semiconductor IP are used by customers to deliver products to

market faster. The company’s Intelligent System Design strategy

helps customers develop differentiated products—from chips to

boards to intelligent systems—in mobile, consumer, cloud, data

center, automotive, aerospace, IoT, industrial and other market

segments. Cadence is listed as one of Fortune Magazine's 100 Best

Companies to Work For. Learn more at cadence.com.

© 2019 Cadence Design Systems, Inc. All rights reserved

worldwide. Cadence, the Cadence logo and the other Cadence marks

found at www.cadence.com/go/trademarks are trademarks or registered

trademarks of Cadence Design Systems, Inc. All other trademarks are

the property of their respective owners.

View source

version on businesswire.com: https://www.businesswire.com/news/home/20190925005362/en/

For more information, please contact: Cadence Newsroom

408-944-7039 newsroom@cadence.com

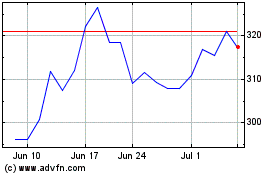

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Mar 2024 to Apr 2024

Cadence Design Systems (NASDAQ:CDNS)

Historical Stock Chart

From Apr 2023 to Apr 2024